3.2 添加设计文件

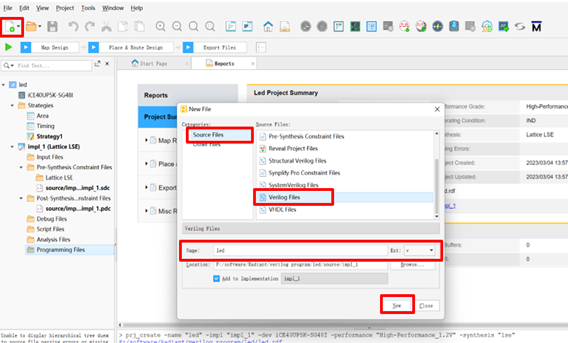

1、选择File→New→File 或 点击工具栏中的New按钮,选择Verilog File文件类型,将文件命名为led,点击New,Radiant软件会新建并打开Verilog文件。

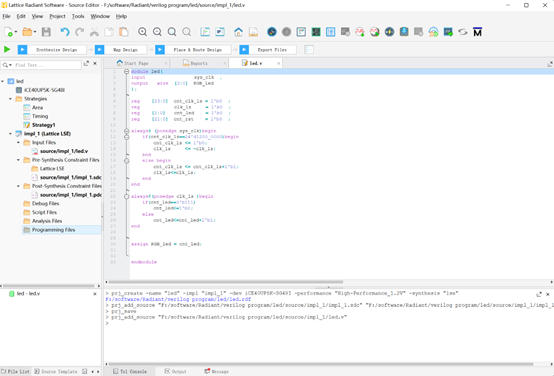

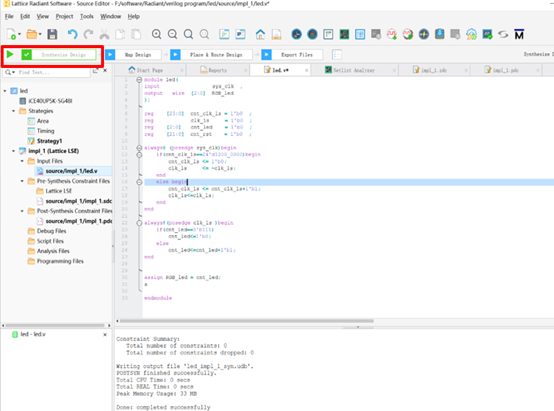

2、在新建的Verilog文件中进行Verilog代码编写、保存,如下图所示,程序源码如下。

源代码:

reg [23:0] cnt_clk_1s = 1'b0 ;

reg clk_1s = 1'b0 ;

reg [2:0] cnt_led = 1'b0 ;

reg [21:0] cnt_rst = 1'b0 ;

always@ (posedge sys_clk)begin

if(cnt_clk_1s==24'd1200_0000)begin

cnt_clk_1s <= 1'b0;

clk_1s <= ~clk_1s;

end

else begin

cnt_clk_1s <= cnt_clk_1s+1'b1;

clk_1s<=clk_1s;

end

end

always@(posedge clk_1s )begin

if(cnt_led==3'b111)

cnt_led<=1'b0;

else

cnt_led<=cnt_led+1'b1;

end

assign RGB_led = cnt_led;

endmodule

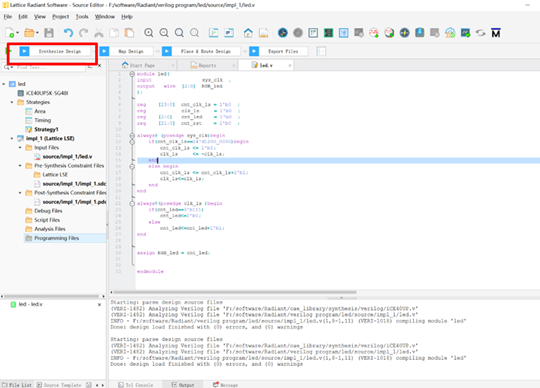

3、选择工具栏中Synthesis Design按钮,如下图所示。

4、Radiant软件会完成分析综合,若设计没有问题,综合Synthesis Design会变成绿色,同时左侧出现绿色对勾。

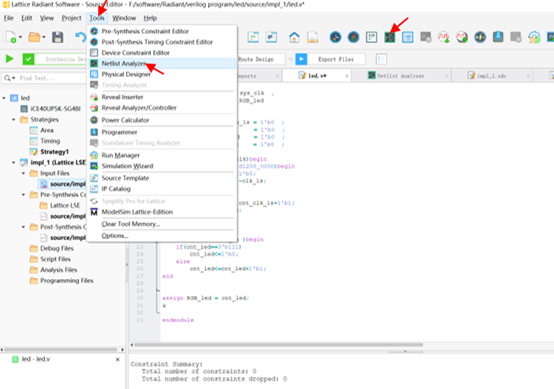

5、分析完成后可以选择工具栏中Netlist Analyzer 或者 Tools→Netlist Analyzer查看电路。

RTL电路图如下